JEDEC and OCP (Open Compute Project Foundation) announce new Chiplet Design Kits for EDA use covering four areas: Assembly, Substrate, Material and Test. Basically, they are a way for chiplet builders to provide – electronically – a standardised chiplet part description to customers. The idea is to pave the way for automating System-in-Package (SiP) design and build using such chiplets. ...

EDA and IP

Synopsys extends Virtualizer IP suite for Arm-based hardware

Embedded World 2025: Synopsys says its Virtualizer Native Execution prototyping tool will accelerate software development for edge devices. It extends the Virtualizer tool suite and model libraries to Arm hardware, allowing virtual prototypes to be built, executed and tested directly on Arm-based machines. The Native Element factor in the new tool means that users can execute virtual prototypes directly on ...

Video: Lee Harrison explains the technology behind full In-System ATPG testing for advanced semiconductors

Watch the video below, where Lee Harrison – Director of Automotive IC Solutions at Siemens EDA – explains the technology behind full In-System ATPG testing for advanced semiconductors Continuous testing and monitoring of devices is required to guarantee optimal performance, reliability and safety throughout their operation, he explains. Tessent In-System Test enables the application of high-quality deterministic test patterns for ...

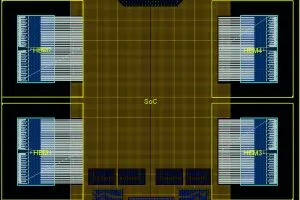

Strategies for optimising chiplet design

Hierarchical planning and parameterised pin region strategies form a smart path to designing chiplets, explains Heiko Dudek. The semiconductor industry is undergoing a transformative shift towards chiplet-based architectures. This is driven by the need for higher functional density and, at the same time, a requirement for cost efficiency in ICs. One innovative approach uses hierarchical device planning and parameterised pin ...

Synopsys expands HAV to address complex chip design

Synopsys has added the HAPS-200 prototyping and ZeBu-200 emulation system to its hardware-assisted verification (HAV) portfolio. Both the HAPs-200 and ZeBu-200 are based on the AMD Versal Premium VP1902 adaptive SoC and built on the company’s emulation and prototyping, or EP-Ready, hardware for use with reconfiguration and optimisation software. ZeBu Server 5 delivers scalability beyond 60bn gates, to target large ...

Tampere Uni leads project to reduce CAD costs for SMEs

Tampere University, along with 11 other partners from various European research institutions and universities, has been awarded €24 to develop a cloud-based IC design platform. The project aims to integrate a wide array of tools and services to make designing chips more accessible to start-ups and SMEs. For many SMEs, the costs and complexities of chip design tools have been ...

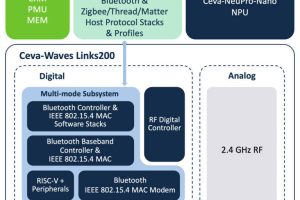

IP adds Bluetooth High Data Throughput to IEEE 802.15.4 radio

Ceva has added Bluetooth High Data Throughput (HDT) to IEEE 802.15.4 for Zigbee, Thread and Matter in radio intellectual property aimed at TSMC’s FFC+ 12nm finfet semiconductor process. “Ceva-Waves Links200 [is] the first turn-key multi-protocol platform IP to support next generation Bluetooth HDT,” claimed Ceva. “High Data Throughput mode more than doubles the speed of traditional Bluetooth, delivering up to ...

TRNG added to Crypto Quantique PUF

Crypto Quantique, a provider of quantum-driven security for the IoT, has boosted the functionality of its semiconductor hardware security IP block, QDID, adding a true random number generator (TRNG) to the physical unclonable function (PUF). The PUF is inherently resilient against side-channel attacks because the source of entropy is quantum-derived, and seeds are read on demand. The QDID PUF is ...

IP meets low latency HPA and AI design demands

Based on Synopsys’ Ethernet and PCIe IP, the Ultra Ethernet IP help developers of AI/HPC infrastructure chips and systems. Hyperscale data centres will need to scale to hundreds of thousands of accelerators and rely on efficient and fast connections to support large language models which process trillions of parameters in large language models for HPC and AI operations, continued Ron ...

Siemens Tech Day: Video Overview of Automotive Semiconductor Tech Day

Watch the video below, providing an overview of the recent Siemens EDA Automotive Semiconductor Tech Day. It examines why semiconductor development is the most important factor for the automotive industry, as a source of differentiation and also for safety, security and autonomous driving… You will see contributions from Lee Harrison, Heiko Dudek, and Stephanie Dournelle from Siemens EDA, and also ...