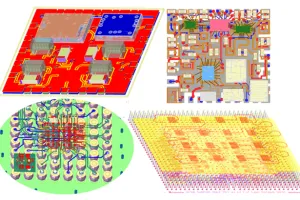

Keysight has combined it Electromagnetic Simulator with Synopsys’ AI-powered RF design migration flow for an integrated design flow to migrate from TSMC’s N6RF+ to N4P process technology. The migration workflow builds on the foundry’s Analog Design Migration (ADM) methodology to streamline the redesign of passive devices and design components to the advanced RF process rules. The collaborative migration workflow leverages ...

EDA and IP

Atlas suite marks MIPS’ drive to co-design

For physical AI at the edge, MIPS has introduced the Atlas Explorer portfolio. The company explained that it allows designers cycle-accurate repeatability of their workload onto a MIPS processor. It provides access to platform IP ahead of silicon availability for evaluation to enable pre-production RTL and for teams to develop optimised hardware and concepts such as digital twins to gain ...

Siemens applies AI across chip and PCB design portfolio

DAC 2025: There was a lot of talk about AI at this year’s DAC but one of the most significant was that Siemens Digital Industries Software has added generative and agentic AI capabilities across its EDA portfolio. The EDA AI system applies across all semiconductor and PCB design suites, including Questra, Tessent, Xpedition, Veloce, Catapult, Calibre, Aprisa and Solido. “It ...

Translation tool tackles optimisation in large SoCs

Designers looking to optimise PPA (power, performance, area) are finding that optimisation engines can render original programmatic timing constraints unusable in their original form. At DAC 2025, Ausdia introduced Timevision OneSource which automatically generates a new version of block-level constraints after optimisation engines have worked on hierarchies, duplicate elements and performed advanced transformation. Such optimisations can save two weeks of ...

Switch fabric scales up data movement for AI

San Francisco: At last year’s DAC, Baya Systems emerged from stealth mode. At this year’s event, the design software company announced a switch fabric technology that is claimed to enable a x100 increase in node density. NeuraScale is designed to overcome critical scaling and data movement challenges in AI infrastructure that are driving advanced SoCs and emerging 3D chiplet-based designs, ...

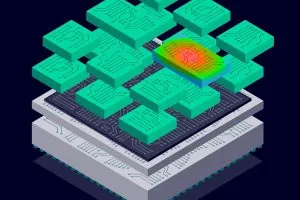

Two software tools target efficient design of 2.5D and 3D ICs

Two software tools, Innovator3D IC and Calibre 3DStress, address chiplet integration and thermal management at the transistor level. Siemens Digital Industries Software announced the duo at DAC 2025. The Innovator3D IC suite advances 3D IC integration using AI to execute chip design and raise productivity, as designers increasingly reintegrate chiplets into high performance substrates, said the company. It enables IC ...

Agentic AI platform automates three stages of design

All three stages of chip design will be automated and accelerated, says Moores Lab AI, which has introduced four design tools using agentic AI. Agentic AI is one of the buzzwords at this year’s DAC in San Francisco. Whereas generative AI generates content, agentic AI is an automation process. It autonomously makes and acts on decisions with little human intervention. ...

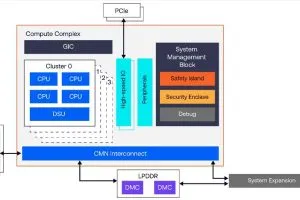

Arm announces pre-integrated AI, safety and security IP for vehicles: Zena CSS

Arm has pre-integrated intellectual property for designers of AI-defined vehicle ICs. “Capabilities like real-time driver monitoring, predictive maintenance and adaptive in-vehicle infotainment, that were once limited to premium models, are becoming the standard across all tiers of new vehicles,” according to the company. “At the same time, automotive development complexity continues to grow, with evolving safety requirements and increasing demands ...

Questa One software uses AI to verify complex chip design

To address the fall in first-time silicon success rates, Siemens Digital Industries Software has announced the Questa One software suite. Consisting of four tools, the suite targets productivity in IC design using AI-powered automation to accelerate verification. According to Abhi Kolpekwar, vice president and general manager, Digital Verification Technologies, Siemens EDA, the increased complexity of asic and FPGA design means ...

Siemens and IFS certify tools

Siemens Digital Industries Software and Intel Foundry have announced tool certifications. Siemens’ Calibre nmPlatform tool is now certified for the Intel 18A PDK. Siemens’ Solido SPICE and Analog FastSPICE (AFS) software tools have been certified for the Intel 18A PDK. Siemens’ Calibre nmPlatform and its Analog FastSPICE (AFS) software, which is part of Siemens’ Solido Simulation Suite offerings, are also ...