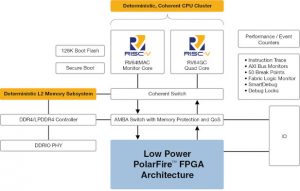

Called ‘PolarFire SoC’, the “architecture brings real-time deterministic asymmetric multiprocessing capability to Linux platforms in a multi-core coherent CPU cluster”, according to the firm, which worked with Risc-V specialist SiFive to create the devices.

Real-time operation is included for safety-critical, system control and trusted execution environments.

It is achieved by turning off CPU branch predictors, converting level 1 cache to tightly integrated memory, ensuring all cores are coherent to the memory subsystem and sharing a coherent memory for message passing.

The four cores execute the RV64GC instruction set. To monitor those, there is a fifth 64bit Risc-V, this time executing the RV64IMAC instruction set. All five can operate coherently.

From existing PolarFire FPGAs, Risc-V versions are inheriting security functions including: DPA-resistant bit-stream programming, anti-tamper, a cryptographical bound supply chain assurance, a physically un-clonable function, a true random number generator and a side-channel resistant crypto-coprocessor.

In addition according to Microchip the processors will have secure boot (128kbyte boot flash), physical memory protection and, on all memories: single-bit error correction and double-bit error detection. THe firm is also claiming Spectre and Meltdown immunity.

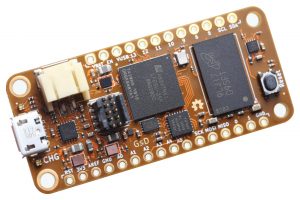

Prior to the chips being available, Antmicro’s Renode open-source build-debug-test framework software can be used and Microchip has created ‘HiFive Unleashed Expansion Board’ to run alongside HiFive’s ‘Unleashed Development Board’ – Microchip has dubbed the two boards together: MPFS-DEV-KIT.

For existing PolarFire FPGAs, Microchip has ‘Mi-V’ 32bit Risc-V soft cores that execute the RV32I (integer) instruction set, some with ‘M’ (miltiply/divide), ‘A’ (atomic instruction) or ‘F’ (single-precision floating point) extensions.

Microchip presented at the ‘Getting Started with RISC-V’ seminar in London last week.

Electronics Weekly

Electronics Weekly