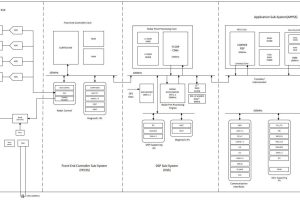

Called AIRisc-Safety, it can now be licensed from the organisation, which also offers customised versions for asic and FPGA integration.

“Certification means that industrial customers directly receive a safety element including a manual and can thus incorporate the AIRisc-Safety into their own chips as a basic element for functional safety”, according to Fraunhofer IMS.

The safety core was developed for the Fraunhofer-lead project Albacopter (pictured) and the automotive research project VE-Diva-IC.

The safety core was developed for the Fraunhofer-lead project Albacopter (pictured) and the automotive research project VE-Diva-IC.

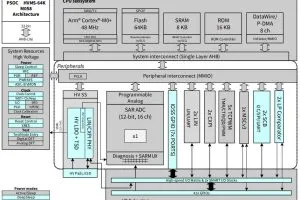

AIRisc was adapted by: monitoring communication interfaces, implementing dual-core lock-step cores, adding error-correcting codes to the memory connections and adding a window watchdog to monitoring software execution.

“A specially developed hardware abstraction layer encapsulates the functionality of the hardware platform and makes it available to the application as a system function,” said Fraunhofer. “With the help of the new microcontroller, for example, the flight attitude of an autonomous drone could be controlled in a fail-safe manner.”

Applications foreseen for the core are LiDAR-based control and data processing units in vehicles, critical infrastructures and health care.

A basic version of AIRisc is available from Github for evaluation.

Find out what the Albacopter and VE-Diva-IC projects are.

Electronics Weekly

Electronics Weekly