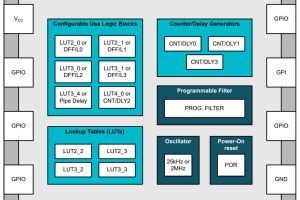

A report by chip test firm iRoC Technologies found that between one in five and one in ten configuration upsets in SRAM devices leads to a logic error.

The iRoc tests used a JEDEC approved methodology that subjects parts to a neutron flux deemed to be equivalent to 7,600 years at sea level. But Rick Padovani, director of high reliability products at Xilinx, said the correlation between the accelerated test and real life is inaccurate. Padovani said that the company’s own experiments to determine the impact of the effect on the reliability of its parts suggests a different figure.

“We’ve compiled [our] data and we do have some correlation now with the [neutron] beam. It would indicate that the results in this report are probably overstated by an order of magnitude,” Padovani said. “If you look at the test results compared to what is seen in the real world – we’ve shipped millions of devices, along with the rest of the industry with microcontrollers and so on – and to date this phenomenon has not shown itself as a reliability problem to any large extent. ”

However, last week Ken O’Neill, director of military and aerospace product marketing at Actel, said: “We’re actually seeing a lot of Japanese customers who have complained that they have had strange behaviour in their devices.”

The debate, which has been ongoing between the SRAM, flash and antifuse FPGA firms for years, looks likely to rumble on. For example, while Actel says the reduced charge on an SRAM cell at smaller geometries makes errors more likely, Xilinx says the smaller transistor size presents a reduced cross section to the neutron flux, so reliability is improved.

Electronics Weekly

Electronics Weekly