Addressing the growing use of AI and high-performance computing, JEDEC has published a new high-bandwidth memory (HBM) DRAM standard: HBM4. It aims to improve the performance, efficiency, and scalability of the memory required to power the next generation of AI, HPC (high-performance computing), and graphics workloads. For example, the next generation AI training and inference systems. HBM4 With transfer speeds ...

JEDEC

JEDEC, OCP design kits progress automated SiP design using chiplets

JEDEC and OCP (Open Compute Project Foundation) announce new Chiplet Design Kits for EDA use covering four areas: Assembly, Substrate, Material and Test. Basically, they are a way for chiplet builders to provide – electronically – a standardised chiplet part description to customers. The idea is to pave the way for automating System-in-Package (SiP) design and build using such chiplets. ...

JEDEC updates Universal Flash Storage and Memory Interface standards

JEDEC – the Solid State Technology Association – is publishing JESD220G: Universal Flash Storage 4.1, an update to the UFS standard. Aimed at applications where power efficiency is essential, UFS 4.1 offers faster data access and improved performance, says the standards body. It also maintains hardware compatibility to UFS 4.0. For example, it will be relevant for mobile applications and ...

Jedec specs JESD230G for improved NAND Flash Interface speeds

JEDEC, the Solid State Technology Association, has published JESD230G, the NAND Flash Interface Interoperability Standard. The standard introduces speeds of up to 4,800 MT/s, as compared to 400 MT/s in the first version of JESD230, which was published in 2011. JESD230G The standards body highlights that JESD230G also adds a separate Command/Address Bus Protocol (SCA). It improves throughput and efficiency ...

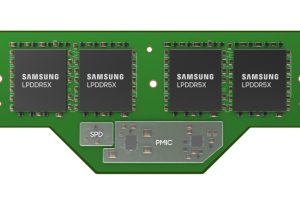

JEDEC publishes LP5CAMM2 thin connector standard for SSDs, GPUs

The JEDEC Solid State Technology Association has announced the PS-007A LPDDR5 CAMM2 Connector Performance Standard, for the “LP5CAMM2” compact form factor. The microelectronics standards body says the connector offers a “standardized modular LPDDR5 solution with ecosystem support”. It contrasts this with the traditional LPDDR5 memory-down approach. Possible applications include solid state drives and GPUs. “Specifically designed for devices that require ...

JEDEC JESD406-5 expands market for “raw card” memory modules

The JEDEC Solid State Technology Association has published its JESD406-5 LPDDR5/5X Serial Presence Detect (SPD) Contents V1.0, supporting the memory module configurations known as “raw cards” (JESD401-5B). This is consistent, says the standards body, with the recently updated contents of JESD401-5B DDR5 DIMM Label and JESD318 DDR5/LPDDR5 Compression Attached Memory Module (CAMM2) Common Standard. JESD406-5 The new publication documents the ...

JEDEC plans advanced memory modules for next-gen AI applications

JEDEC has unveiled its plans for advanced memory modules to enable future high-performance computing and AI applications. Specifically, the standards body has revealed details about its standards for DDR5 Multiplexed Rank Dual Inline Memory Modules (MRDIMM) and a next-generation Compression-Attached Memory Module (CAMM) for LPDDR6. The aim is to provide “unparalleled bandwidth and memory capacity”. Both projects are in development ...

JEDEC publishes JESD405-1B CXL memory module label standard

JEDEC has published “JESD405-1B JEDEC Memory Module Label – for Compute Express Link (CXL) V1.1”, providing detailed guidelines for CXL memory modules. These modules are described as “end-user friendly hot pluggable assemblies” and are for data centres and similar server applications. They conform to SNIA (Storage Networking Industry Association) EDSFF form factors E1.S and E3.S. CXL Specifically, JESD405-1B defines the ...

JEDEC JEP30 specs Part Model Guidelines for Chiplet Integration

JEDEC has published a new release of the JEP30 Part Model Guidelines, including reference documents and related XML Schema files. Working in collaboration with the Open Compute Project Foundation (OCP), the electronics standards body says it has combined the capabilities and open standards of OCP’s Chiplet Data Extensible Markup Language (CDXML) into its JEP30 Guidelines. In prospect, it suggests, is ...

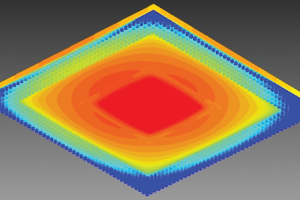

Sponsored Content: Five tips for predicting component temperatures

Historically, component temperature has been correlated with reliability, with early studies relating field failure rates to steady-state component temperature. More recently, physics-based reliability prediction has related failure rates of electronic assemblies to the magnitude of temperature change over an operational cycle (power-on, power-off, power-on…) and rate of temperature change, both of which are influenced by steady-state operating temperature. Electronics failures ...

Electronics Weekly

Electronics Weekly