French research lab Leti has teamed up with low-volume chip firm CMP to provide 200mm multi-project wafers (MPWs) including non-volatile memory OxRAM (Oxide-based Resistive Memory). “Leti’s integrated silicon memory platform is developed for backend memories and non-volatility associated with embedded designs,” said the lab. “The technology platform will be based on titanium-doped hafnium oxide [HfO2/Ti] active layers.” The OxRAM is ...

EDA and IP

C-SKY Micro licenses UltraSoC

C-SKY Microsystems licenses UltraSoC’s embedded analytics technology for use in C-SKY SoCs

RS adds free IoT design tools download to DesignSpark

RS Components is working with a start-up company that develops ‘middleware’ software for Internet of Things (IoT) projects and applications. The distributor’s agreement with Zerynth will mean its IoT development environment will be available via a portal on the RS DesignSpark engineering community, allowing customers to download the tools. Zerynth has developed a suite of software tools for programming 32-bit ...

Joining forces to strengthen IIoT

Two president-CEOs in a room does not often produce the bonhomie witnessed on the Mentor Graphics booth at DAC 2018, observes Caroline Hayes The adage ‘buyer beware’ would seem not to apply in the case of the acquisition of Mentor Graphics by Siemens PLM in March 2017. Mentor Graphics’ president and CEO, Wally Rhines and Siemens Product Lifecycle Management (PLM) ...

Zuken updates CR-8000 system-level PCB design environment

Zuken has released CR-8000 2018, an updated version of its system-level 2D/3D PCB design environment. The focus of CR-8000 2018, according to the firm, is on enabling front-loading of design constraints and specifications to the design creation, coupled with placement and routing capabilities for physical layout. “With smart applications adding complexity to the product design process, controlling adherence of PCB ...

EDA embraces standard to streamline IC test and verification

Caroline Hayes finds out about the Accellera effect at DAC 2018 As well as EDA, IP and SoC companies, this year’s DAC was distinguished by the number of industry bodies that were promoting their particular brand of technology and establishing standards which the industry should follow. Accellera , the body promoting system level design, modelling and verification standards, was linked ...

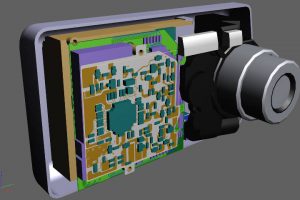

Swindon Silicon Systems launches IC Builder

Swindon Silicon Systems has launched IC Builder – a new way for design engineers to visualise what their ASIC/MEMS solution may look like for their application and discuss the results and the process required to implement the design. “There are several reasons for taking the ASIC route and high on the list is the ability to integrate high levels of ...

Green Hills supports Automotive Grade Linux with secure RTOS

Green Hills Software has announced that its Integrity Multivisor secure virtualization and advanced development tools now support implementation of Automotive Grade Linux (AGL) on different 64-bit automotive grade SoCs. This means that AGL applications can be added to automotive systems meeting the ISO 26262 safety levels. So that AGL-based connected car applications will run in secure partitions alongside safety-critical and security-critical functions ...

DAC: Cadence builds its cloud-based design world

Cadence Design Systems announces a cloud-based chip and system design tool portfolio.

TSMC refines N7 technology; N5 in development

DAC 2018: Foundry TSMC confirmed that it has refined the N7 technology it introduced at last year’s DAC, with N7+, using EUV layers to realise a smaller, denser standard cell to reduce power requirements and increase density by up to 20%. The denser standard cell increases reliability, exploiting EUV layers for greater accuracy in the design, says the company. Willy ...

Electronics Weekly

Electronics Weekly