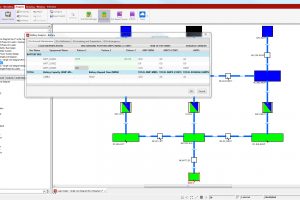

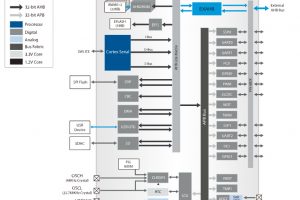

For software development without final silicon, Cadence has launched FPGA-based hardware that can simulate SoCs with up to a billion gates. Called Protium X1, it is intended for debugging software intended to run on SoCs that have yet to be fabbed – for AI, 5G mobile and graphics processors, for example. It can run a 1bn gate design at around 5MHz, ...

EDA and IP

Analyser software uses digital twin for aero certification

Software developed by Mentor is designed to help aircraft projects meet electrical load compliance. The Capital Load Analyzer software reduces risk in aerospace electrical compliance and certification. Anthony Nicoli, IES director of Aerospace and Defense, Mentor explained that the increased information and displays used in the aircraft cockpit for flight control and in passenger in-flight entertainment systems, has increased the ...

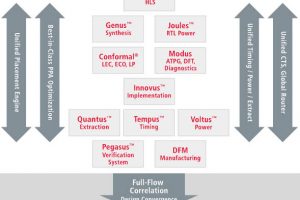

Cadence design and sign-of tools for 7nm Arm Cortex-A77

Cadence has announced design and sign-off tools for Arm’s new Cortex-A77 CPU on 7nm processes. The 7nm rapid adoption kit (RAK) provides an RTL-to-GDS flow using Arm 7nm POP IP libraries. “We worked with Arm to optimise our digital implementation and sign-off solutions for the Cortex-A77 so customers can create 7nm designs that meet PPA [power, performance and area] goals,” ...

Toolchain supports RISC-V cores

Swedish embedded software provider, IAR Systems, has recognised the increased adoption of RISC-V-based designs, with the introduction of a C/C++ compiler and debugger toolchain to support RISC-V cores. The first version of IAR Embedded Workbench for RISC-V has been internally tested and the company reports that the C/C++ compiler improves code density, compared to other tools currently available, generating code that ...

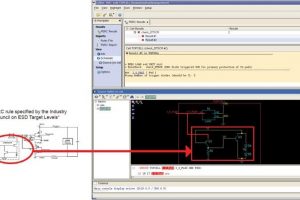

Mentor tools for 5nm TSMC finfet process

TSMC has certified a suite of Mentor Calibre nmPlatform design tools for its 5nm finfet process, including nmDRC, nmLVS, YieldEnhancer, PERC (pictured) and Analog FastSPICE (AFS) Platform software. “For example, Calibre PERC reliability verification solution on TSMC’s 5nm FinFET technology is engineered to help enhance product reliability by making leakage checks available for full chip designs,” said Metor. “Running these checks can ...

Agile Analog raises $5 million

Agile Analog announces it has closed its latest Pre-A funding round with Delin Ventures

Interview: SamacSys CEO on component modelling, EDA and engineering frustrations

We talk to Alex MacDougall, founder and CEO of SamacSys, about EDA tools and component libraries.

FlexLogix introduces inference engine

FlexLogix announces inference-optimized nnMAX clusters to develop the InferX X1 edge inference co-processor

Asic service offers RISC-V for IoT and AI

Taiwan asic design house Faraday Technology is offering RISC-V processor IP for chips aimed at AI and IoT. “This solution encompasses system-level design services, such as RISC-V core IP integration, SoC design verification, as well as a reference design kit consisting of RTOS and peripherals drivers,” said the firm, adding that it has already enabled mass production of RISC-V based AI ...

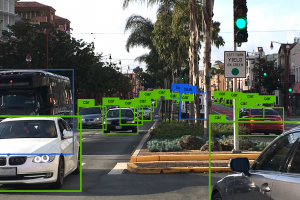

Comment: On autonomous driving and seizing the tech transfer opportunity

The development of autonomous vehicles provides opportunities for innovative electronics businesses

Electronics Weekly

Electronics Weekly