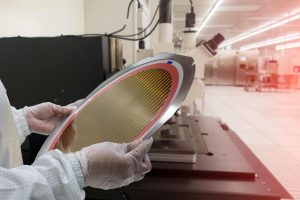

Berkshire-based Sondrel is offering design services for 5nm foundry processes, building on 7nm designs, of which it has taped out a number. “We are one of the few design companies working on Samsung and TSMC at these advanced nodes,” said CEO and founder Graham Curren, enumerating: “Firstly, because they are invariably extremely large and complex with billions of gates in a ...

EDA and IP

Mentor changes its name to Siemens EDA

Since its acquisition in 2017, EDA software company, Mentor, has styled itself ‘Mentor, a Siemens company’. From January, 2021, it will change its name to Siemens EDA. Announcing the name change, Joe Sawicki, executive vice president of IC-EDA, Siemens EDA (pictured), said that the name brings EDA software, simulation, mechanical design, manufacturing, cloud, IoT and low code technology under a ...

Redtree Solutions offers Agile Analog IP across Europe

Asic and foundry service specialist, Redtree Solutions has signed an agreement with Agile Analog, making the latter’s configure IP available as part of the RedASIC custom chip design service. Redtree offers turnkey asic services, including offshore and local design, analogue, RF, mixed and digital design, foundry prototyping to production services, packaging and testing for both prototyping and volume production and ...

AdaCore tools for Wind River Helix virtualisation

AdaCore has launched a new edition of its Gnat Pro Ada, C and C++ development tool suites to support Wind River’s Helix virtualisation platform. Gnat Pro comes in separate packages for Ada or C/C++, and “enhances Helix platform’s ability to consolidate mixed-criticality aerospace, defence and automotive applications onto a certifiable platform”, according to AdaCore. “Helix platform customers will experience a consistent ...

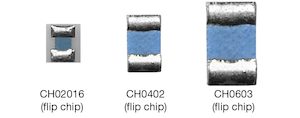

Simulation models for microwave resistors reach 67GHz

Vishay has announced broadband Microwave Global Models for its Sfernice CH series resistors in 02016, 0402 and 0603 case sizes. The models are available within the Modelithics Complete Library and ‘mmWave & 5G’ Library. “Modelithics’ measurement-based models offer part value, substrate, and solder pad scalability,” according to Vishay. “They are validated up to 67GHz and accurately predict parasitic effects based on the model parameter ...

Moortec bought by Synopsys

Moortec, the Plymouth on-chip monitoring IP specialist, has been bought by Synopsys. Synopsys rolled out its Silicon Lifecycle Management (SLM) platform last month and the Moortec technology adds an important element to provide a broad range of monitors and sensors for more detailed visibility into the chip’s operation. Moortec’s PVT sensors are claimed to be the most advanced in the industry and represent ...

Network software for Tessent TestKompress simplifies DFT flow

To meet the increasing size of ICs, required to accommodate the integration of billions of transistors in order to deliver the performance required for tasks such as AI and autonomous vehicles, Mentor has announced Tessent Streaming Scan Network software for its Tessent TestKompress scan test tool. The larger IC design sizes and increased complexity has led to a rise in ...

UK design: 30bn transistor chip tapes out at Sondrel

Berkshire-based Sondrel has tape-out of its largest chip design for a customer – with a 500mm2 footprint, over 30 billion transistors, 40 million flip-flops, and 23 thousand pads for I/O, power and ground. Up to 200 engineers were working on it simultaneously at times, according to the company. “This initially started out as a design for 28nm technology,” said Sondrel director ...

Embedded Workbench adds support for position-independent RH850 code for automotive

IAR Systems Embedded Workbench C/C++ compile and debug toolchain can now generate position-independent code and position-independent data for Renesas’ RH850 automotive MCUs. “The added functionality is useful in systems where applications are loaded dynamically,” according to IAR. “When using position-independent code and read-only data [ROPI], the compiler will generate code that uses PC-relative references for addressing code and read-only data. ...

riscvOVPsim gets Risc-V vector instructions

Imperas has extended its Risc-V reference model and simulator to cover forthcoming vector instructions and to support coverage-driven verification analysis. Called riscvOVPsim, the enhanced version including a vector test suite is freely available for commercial use from Open Virtual Platforms, and a base version is available free from GitHub. “The upcoming ratification of the Risc-V vector instruction extension offers system designers flexibility ...

Electronics Weekly

Electronics Weekly