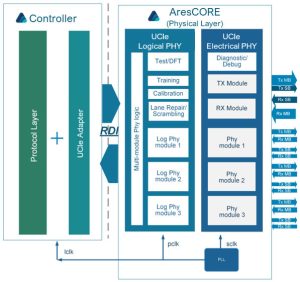

“This complete PHY and controller subsystem, developed with TSMC [using] TSMC’s CoWoS 2.5D silicon-interposer-based packaging, delivers a bandwidth density of 8Tbit/s/mm,” said Alphawave. It supports “PCIe, CXL, AXI-4, AXI-S, CXS, and CHI, features live per-lane health monitoring, and operates at 24Gbit/s”.

The test chip has been validated against UCIe specifications, across typical, slow and fast process conditions, across design voltage and across design temperature, and it meet margins for link, TXIO, and RXIO loopback, according to the company, which added that it complies with UCIe rev 2.0, and includes JTAG, BIST, DFT and KGD (known good die) capabilities.

Applications are foreseen in hyperscale data centres, high-performance computing.

Find the web page here

Electronics Weekly

Electronics Weekly