However, the semiconductor industry continues to deliver incredible advances in IC capabilities. The most successful companies continually refine and optimize all aspects of chip design and fabrication, including the increasingly important design-for-test (DFT).

DFT ranges from insertion and verification of test logic during RTL design all the way to failure analysis of failed fabricated products. Advanced DFT strategies ensure not only that a device meets quality and reliability requirements, but also helps to improve yield, reduce costs, and get the product to market faster. So what are the elements of an advanced, smart DFT strategy? How do you go beyond finding a solution that does little more than the basic purpose of DFT (detecting manufacturing defects)?

DFT has seen lively and productive research and development for several decades. Breakthroughs such as embedded deterministic test (EDT) in 2004 and other advances in DFT have continued to keep test costs from over-taking the budget and helped to improve the test quality of ICs across the board.

Let’s look at some of the most significant areas of DFT research and development that have led to solutions for today’s most challenging designs, like extremely large artificial intelligence (AI) processors that require hierarchical plug-and-play methodologies, and automotive applications that need very high manufacturing test quality and in-system test capabilities.

Better defect detection

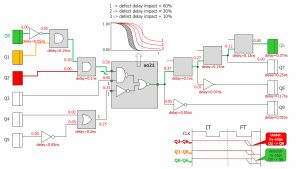

Figure 1. Timing-aware ATPG combined with cell-aware test to find small delays considering the longest paths and delays within cells.

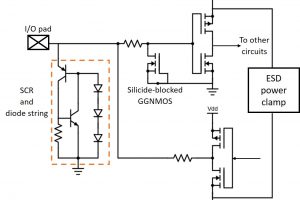

First, DFT must catch defects in manufactured silicon and ensure that a part will operate correctly once it’s placed in-system. We can make basic predictions about the expected defect level depending on the process yield. If fault coverage is too low, you ship bad parts and your business suffers. What is too low? Well, for ICs in automotive safety systems, 99% is too low. For any IC in a safety-critical role, the fault coverage needs to be much higher, requiring the use of cell-aware fault models that can target potential defects within the technology cells. Major semiconductor companies, including AMD (Hapke, 2014) have seen dramatic improvements in fault coverage with cell-aware test. Cell-aware test and advanced fault models have been expanded to include new types of bridge, opens, cell-aware/timing-aware (see Figure 1 above), and cell-neighborhood tests. This so-called “automotive-grade” test has been vetted by the likes of Intel (Howell, 2018) and ON Semiconductor (Maxwell, 2017) in published research papers.

Scan test is just one part of DFT. Built-in-self-test is a necessary companion in many of today’s designs. Memory BIST, which detects failures in embedded memories and their interface logic, needs to manage designs with a huge number of memory instances. This takes a DFT tool that works efficiently in a hierarchical DFT methodology. Hierarchical DFT for designs of this scale requires fully automated solutions that can work with higher-level user input across all parameters (test time, area consumption, power consumption, etc.).

Numerous published case studies show the benefits of hierarchical DFT which generates patterns at the block level and directly reuses those patterns at the top level. Some of the foremost benefits include:

- 10X performance gain in ATPG, diagnosis, and pattern verification;

- Up to 2x pattern count reduction;

- The removal of DFT from the critical path; and

- The enabling of core re-use.

Detecting more faults usually requires larger sets of test patterns, which increases demand on compute resources, test time and cost. There are several strategies to manage higher test volumes. One is using hierarchical DFT. A new kind of test point was introduced that dramatically reduces pattern sizes. Companies like Broadcom (Konuk, 2015) have used these new test points to control the growing test pattern counts. An even newer technology for logic BIST, called LBIST Observation Scan Technology, was designed specifically to improve in-system test speed for automotive devices.

Improved yield

DFT doesn’t end with detecting manufacturing defects. It also works to improve the manufacturing process and increase yield, which has a direct impact on business. Manufacturing test collects a massive amount of data from failing tests, revealing valuable information about the mechanisms that cause the circuit to fail. This data needs to be analyzed through scan diagnosis to suss out the true causes and locations of circuit failures. Scan diagnosis improves the success of physical failure analysis used to validate the defect mechanism. Advanced scan diagnosis has been used by foundries like GLOBALFOUNDRIES to find root causes of failures more efficiently (Benware, 2012).

Fixing a systematic yield problem requires data about the failure mechanisms on a whole population of failing die across wafers and lots. Performing volume scan diagnosis, an advanced technique that uses statistics and machine learning, speeds yield ramp for new processes and improves yield for mature processes. This technology is in use in many successful companies.

Streamlined DFT flow

All the DFT technologies available today will fail to enhance your competitiveness if they are difficult to integrate into reliable design flows. Using a hierarchical DFT flow, which is probably the biggest single change you can make to reduce overall DFT implementation effort, has been widely adopted among companies across the semiconductor industry. Amazon (Trock, 2016) and Samsung (Shin, 2019) have both presented accounts of dramatic improvements in all aspects of DFT with a hierarchical methodology.

Another strategy to improve the DFT flow is to push more of the DFT work into the RTL phase. This requires DFT flows to merge with any standard front-end design flow, and for DFT tasks to be automated and repeatable. Creating a reliable DFT flow is easier if all the DFT technologies are built on a shared database. A unified DFT platform can operate as an “intent-driven” environment, reducing the complexity of the DFT flow and accelerating time-to-market. Both eSilicon (Mentor press release, 2019) and Broadcom (Mentor press release, 2020; ITC, 2019) presented results showing 50% reductions in implementation time with hierarchical DFT and a unified DFT platform.

Figure 2. Tessent Connect provides the type of platform necessary with current levels of complexity and integration.

A winning DFT strategy is not just dependent on DFT tools, but also on the ecosystem around them. Partnerships ensure scalable technologies that work in any design flow. For example, for cell-aware test, you can make your own cell-aware models, but Arm now provides cell-aware library models for both ATPG and diagnosis. There are existing reference design flows for Mentor DFT with Arm and Samsung. ATE suppliers Teradyne and Advantest support over-the-cloud tester access and 1149.10 high-speed IO scan test in partnership with Mentor.

Summary

To remain competitive, your DFT strategy should offer more efficiency, better test coverage, smoother integration with flows and function system requirements, faster and more accurate analysis of production test results, and greater flexibility and usability. Investing in a reliable, market-leading DFT platform will confer an enduring business advantage for products today and the new challenges of tomorrow.

Further reading

For more information, download this whitepaper: “How to maximize your competitiveness in the semiconductor industry using advanced DFT”.

Ron Press, of Mentor, a Siemens Business

Electronics Weekly

Electronics Weekly