All three stages of chip design will be automated and accelerated, says Moores Lab AI, which has introduced four design tools using agentic AI. Agentic AI is one of the buzzwords at this year’s DAC in San Francisco. Whereas generative AI generates content, agentic AI is an automation process. It autonomously makes and acts on decisions with little human intervention. ...

design tools

DVCon Europe 2025

The Design and Verification Conference & Exhibition Europe (DVCon Europe), hosted by Accellera Systems Initiative, has announced the 12th edition of the show, to take place in Munich on 14th and 15th October 2025, with SystemC Evolution Day on the 16th.

Synopsys extends Virtualizer IP suite for Arm-based hardware

Embedded World 2025: Synopsys says its Virtualizer Native Execution prototyping tool will accelerate software development for edge devices. It extends the Virtualizer tool suite and model libraries to Arm hardware, allowing virtual prototypes to be built, executed and tested directly on Arm-based machines. The Native Element factor in the new tool means that users can execute virtual prototypes directly on ...

Synopsys expands HAV to address complex chip design

Synopsys has added the HAPS-200 prototyping and ZeBu-200 emulation system to its hardware-assisted verification (HAV) portfolio. Both the HAPs-200 and ZeBu-200 are based on the AMD Versal Premium VP1902 adaptive SoC and built on the company’s emulation and prototyping, or EP-Ready, hardware for use with reconfiguration and optimisation software. ZeBu Server 5 delivers scalability beyond 60bn gates, to target large ...

Embedded World: Debug and trace for S32N55 vehicle processor

Programmierbare Logik & Systeme is offering debug and trace for NXP’s S32N55 16 core software-defined vehicle processor, announced yesterday. It is included in the 2024 version of UDE, the company’s universal debug engine. With UDE “the Cortex-R52 main cores and the Cortex-M7 auxiliary cores are all visible and can be controlled from one common debugger user interface”, according to PLS. ...

Training-grade PDK for 2nm gate-all-around ICs

Imec has launched an early-access process design kit for the N2 (2nm ICs) node. “The PDK will enable virtual digital designs in imec’s N2 technology, including backside power delivery network,” according to the Belgion semiconductor research lab. “This will give academia and industry the tools to train the semiconductor experts of tomorrow and enable the industry to transition their products ...

DVCon Europe 2024

The Design and Verification Conference in Europe (DVCon Europe) covers the application of languages, tools and intellectual property for the design and verification of electronic systems and ICs. Chip architects, design and verification engineers, and IP integrators can explore the latest methodologies, techniques, applications and demonstrations for the practical use of EDA solutions for electronic design. The two-day event includes ...

Axivion adds MISRA C++ 202x rules to static code analysis

Axivion has added checks for MISRA C++ 202x rules with the release of its Axivion Suite 7.5 code analysis tools. “Especially when developing safety-critical embedded systems, compliance with the latest coding standards is a must to ensure code quality throughout the whole development process,” according to the company. “Now Axivion Suite 7.5 safeguards compliance with several new MISRA C++ 202x ...

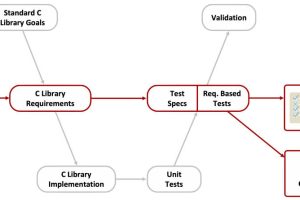

Verifiy all versions of the C standard library specification

Solid Sands is now qualifying “all versions of the C standard library specification, not just a sub-set that is commonly used or a sub-set that fits on a restricted embedded target” following an update to its SuperGuard requirements-based test suite for C standard libraries. “Based on the experience of SuperGuard being used in library qualification projects as well as feedback ...

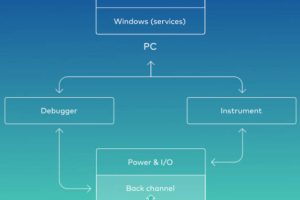

JavaScript tool automates instrumentation for embedded system development

London embedded systems design and test house Bermondsey Electronics has launched what it describes as an “integration verification engine” that automates the operation of networkable instrumentation to exercise a device-under-test (DUT) and verify that its hardware and software are functioning together as intended. Called Believe, and based on JavaScript, it “can also be used for continuous integration and end-of-line quality ...

Electronics Weekly

Electronics Weekly