Designers looking to optimise PPA (power, performance, area) are finding that optimisation engines can render original programmatic timing constraints unusable in their original form. At DAC 2025, Ausdia introduced Timevision OneSource which automatically generates a new version of block-level constraints after optimisation engines have worked on hierarchies, duplicate elements and performed advanced transformation. Such optimisations can save two weeks of ...

Design Software

Switch fabric scales up data movement for AI

San Francisco: At last year’s DAC, Baya Systems emerged from stealth mode. At this year’s event, the design software company announced a switch fabric technology that is claimed to enable a x100 increase in node density. NeuraScale is designed to overcome critical scaling and data movement challenges in AI infrastructure that are driving advanced SoCs and emerging 3D chiplet-based designs, ...

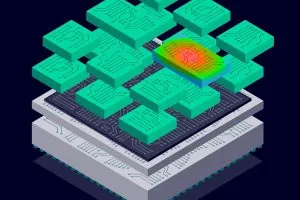

Two software tools target efficient design of 2.5D and 3D ICs

Two software tools, Innovator3D IC and Calibre 3DStress, address chiplet integration and thermal management at the transistor level. Siemens Digital Industries Software announced the duo at DAC 2025. The Innovator3D IC suite advances 3D IC integration using AI to execute chip design and raise productivity, as designers increasingly reintegrate chiplets into high performance substrates, said the company. It enables IC ...

Synopsys extends Virtualizer IP suite for Arm-based hardware

Embedded World 2025: Synopsys says its Virtualizer Native Execution prototyping tool will accelerate software development for edge devices. It extends the Virtualizer tool suite and model libraries to Arm hardware, allowing virtual prototypes to be built, executed and tested directly on Arm-based machines. The Native Element factor in the new tool means that users can execute virtual prototypes directly on ...

Synopsys expands HAV to address complex chip design

Synopsys has added the HAPS-200 prototyping and ZeBu-200 emulation system to its hardware-assisted verification (HAV) portfolio. Both the HAPs-200 and ZeBu-200 are based on the AMD Versal Premium VP1902 adaptive SoC and built on the company’s emulation and prototyping, or EP-Ready, hardware for use with reconfiguration and optimisation software. ZeBu Server 5 delivers scalability beyond 60bn gates, to target large ...

Scope-like data visualisation for Segger SystemView

Segger has added an oscilloscope-like window to its SystemView embedded system analysis software to record variable data alongside runtime events. Called DataPlot, its graphs are synchronised with SystemView’s Timeline and CPU Load windows. Data can be sent in fixed point or floating-point formats and multiple variables can be recorded – each identifiable by a descriptive name and a different color ...

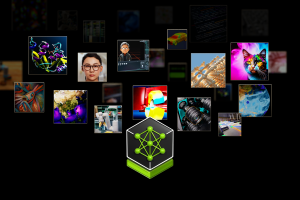

Nvidia offers blueprints from which to develop generative AI applications

Nvidia has announced pre-trained, customisable AI workflows for creating customer service avatars, for data-mining pdf documents, and for virtual drug screening. They are the first three ‘NIM Agent Blueprints’, which the company said will be a catalogue of products to jump-start developers creating applications based on AI agents. They include sample applications built with Nvidia’s ‘NeMo’, ‘NIM’ and partner micro-services, ...

Embedded World: Debug and trace for S32N55 vehicle processor

Programmierbare Logik & Systeme is offering debug and trace for NXP’s S32N55 16 core software-defined vehicle processor, announced yesterday. It is included in the 2024 version of UDE, the company’s universal debug engine. With UDE “the Cortex-R52 main cores and the Cortex-M7 auxiliary cores are all visible and can be controlled from one common debugger user interface”, according to PLS. ...

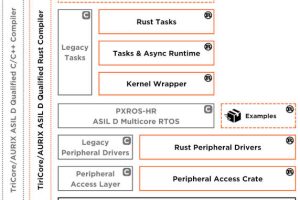

Embedded World: ASIL D qualified Rust compiler for Infineon TriCore processors

Infineon has lined up a Rust programming language compiler for two of its TriCore architecture processor families: the existing TC3x and forthcoming TC4x. “Rust, with its unique memory safety features, has emerged as a viable complement or potential substitute for C/C++ in automotive software development,” according to the company. Working with Infineon, HighTec EDV-Systeme has released an ISO 26262 ASIL ...

Nvidia packages inference to deliver generative AI for healthcare

Optimised packages of AI models and workflows with API have been packaged as NIMs (Nvidia Inference Microservices) which developers can use as building blocks to develop generative AI for healthcare, from drug discovery, med-tech and digital health products. Nvidia announced 25 NIMs at its developer conference, GTC 2024, offering advanced imaging, natural language and speech recognition, digital biology generation, prediction ...

Electronics Weekly

Electronics Weekly