Keysight has combined it Electromagnetic Simulator with Synopsys’ AI-powered RF design migration flow for an integrated design flow to migrate from TSMC’s N6RF+ to N4P process technology. The migration workflow builds on the foundry’s Analog Design Migration (ADM) methodology to streamline the redesign of passive devices and design components to the advanced RF process rules. The collaborative migration workflow leverages ...

DAC

Stay updated on the latest from the Design Automation Conference (DAC) — the leading event for professionals in electronic design automation, silicon design, IP, embedded systems, and software. DAC brings together researchers, engineers, and industry leaders to explore innovations across chip design, AI/ML acceleration, system architecture, verification, and more. With a rich programme of technical papers, keynotes, panels, and exhibits, DAC serves as a critical hub for advancing the future of semiconductor and system design. Discover insights, breakthroughs, and product announcements from one of the most influential conferences in the semiconductor ecosystem.

Atlas suite marks MIPS’ drive to co-design

For physical AI at the edge, MIPS has introduced the Atlas Explorer portfolio. The company explained that it allows designers cycle-accurate repeatability of their workload onto a MIPS processor. It provides access to platform IP ahead of silicon availability for evaluation to enable pre-production RTL and for teams to develop optimised hardware and concepts such as digital twins to gain ...

Siemens applies AI across chip and PCB design portfolio

DAC 2025: There was a lot of talk about AI at this year’s DAC but one of the most significant was that Siemens Digital Industries Software has added generative and agentic AI capabilities across its EDA portfolio. The EDA AI system applies across all semiconductor and PCB design suites, including Questra, Tessent, Xpedition, Veloce, Catapult, Calibre, Aprisa and Solido. “It ...

What caught your eye? (3D IC design, Robotaxi, Accelerometers, SOOP)

This week we're talking about 2.5D and 3D IC design, the robotaxi market, a rush of accelerometers, and sampling broadband satcom signals for navigation purposes...

Translation tool tackles optimisation in large SoCs

Designers looking to optimise PPA (power, performance, area) are finding that optimisation engines can render original programmatic timing constraints unusable in their original form. At DAC 2025, Ausdia introduced Timevision OneSource which automatically generates a new version of block-level constraints after optimisation engines have worked on hierarchies, duplicate elements and performed advanced transformation. Such optimisations can save two weeks of ...

DAC 2026

DAC moves to Long Beach, southern California for 2026. The exhibition and conference covers chips to systems with education, exhibits, training and networking opportunities for designers, researchers, tool developers and vendors. It is of interest to system designers and architects, logic and circuit designers, validation engineers, CAD managers, senior managers and executives, and researchers and academicians from leading universities. The ...

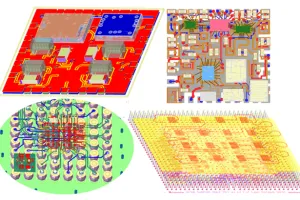

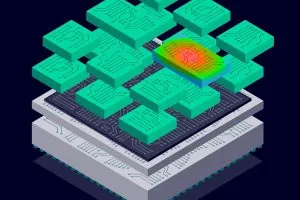

Two software tools target efficient design of 2.5D and 3D ICs

Two software tools, Innovator3D IC and Calibre 3DStress, address chiplet integration and thermal management at the transistor level. Siemens Digital Industries Software announced the duo at DAC 2025. The Innovator3D IC suite advances 3D IC integration using AI to execute chip design and raise productivity, as designers increasingly reintegrate chiplets into high performance substrates, said the company. It enables IC ...

CHIIPS Podcast #10 – DAC insights from professor Helen Hai Li, Duke University

DAC, the Design Automation Conference, is running in San Francisco this week, and Caroline Hayes is talking to Helen Hai Li, a professor at Duke University and the chair of DAC. It’s the latest episode of the Electronics Weekly podcast, CHIIPS (Caroline Hayes’ Industry Insights Podcasts). Listen to the latest podcast episode » You can hear the professor’s plans for ...

VLSI Symposium: 7bit 150Gsample/s DAC on 5nm CMOS

Imec built a 7bit 150Gsample/s digital to analogue converter using 5nm finfet CMOS. Revealed at the Symposium on VLSI Technology and Circuits in Kyoto, it achieves data rates of up to 300 Gbit/s using PAM-4 modulation, said the Belgian research institute, which is aiming it at data centres. “PAM-4 has emerged as the preferred modulation scheme in data centres, enabling ...

DAC 2025

An international conference and exhibition with presentations by approximately 200 of the leading and emerging companies in design tools and chip design. Keynotes, presentations and technical sessions cover : Artificial Intelligence/ Machine Learning (AI/ ML) Automotive Design Services Design on Cloud Electronic Design Automation (EDA) Embedded Systems and Software (ESS) Intellectual Property (IP) Security/Privacy The conference is sponsored by the ...

Electronics Weekly

Electronics Weekly